無電容的3D DRAM,潛力無限

自1966年被IBM研究中心的Robert H. Dennard發明至今,動態隨機存取存儲器(DRAM)已經經過了數十年的發展,並成為存儲器市場最大的細分領域,佔據了58%的存儲器市場規模。

憑借著經濟、可靠、高效等特點,DRAM被廣泛運用於大容量的主存儲器。2018年,DRAM的市場規模就已達到1000億美元,根據IC Insights最新預測,預計到2026年全球DRAM市場規模甚至有望達到1219億美元左右。

然而技術的快速更迭讓DRAM稱霸存儲市場的同時,也讓它陷入了發展的瓶頸時期。在芯片小型化、集成化的發展趨勢下,DRAM的缺點開始不斷被“放大”,傳統的DRAM已經難以滿足當前的需求,在此背景下,人們開始把目光轉向新型DRAM。

3D 堆疊開啟DRAM新未來

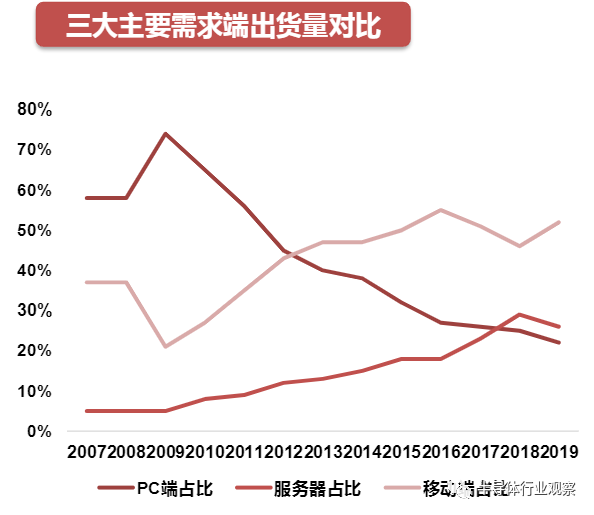

當前,DRAM主要需求來源分別為PC端、移動端、服務器端,其中PC端佔比12.6%,移動端佔比37.6%,服務器佔比 34.9%,三者佔總需求近90%。

從目前發展事態來看,PC端已經進入了存量替代市場,出貨穩定,對DRAM的需求也趨於穩定。但隨著5G熱潮的到來,移動DRAM和服務器DRAM需求變得旺盛,DRAM迎來了“芯”拐點,智能手機帶來的出貨增長以及物聯網、雲服務、商用服務器、數據中心的強勁增長,成為拉動DRAM需求的主力軍。此外,DRAM作為自動駕駛技術中不可或缺的一部分,車用DRAM也將成為未來的新增量。

圖片來源:方正證券

然而,龐大的需求端下,是人們不斷增長的對高容量、高性能、小存儲單元尺寸以及低功耗存儲設備需求,這也使得DRAM在帶寬和延遲方面的挑戰更為緊迫,帶寬指的是可以寫入內存或可以從中讀取的數據量,而延遲是對內存的請求與其執行之間的時間間隔。受限於傳統計算機體系的馮-諾依曼架構,存儲器帶寬與計算需求之間的存儲牆問題日益突出,成為當今計算中的最大問題之一。

一般來說,計算機中的 DRAM 存儲單元由單個晶體管和單個電容器製成,即所謂的 1T1C 設計。這種存儲單元在寫入時打開晶體管,電荷被推入電容器 (1) 或從電容器 (0) 去除;讀取時則會提取並度量電荷。該系統速度超級快,價格便宜,並且功耗很小,但它也有一些缺點。

DRAM作為一種易失性的、基於電容的、破壞性讀取形式的存儲器,在讀取的時候會消耗電容器的電量,因此讀取就要將該位寫回到內存中。即使不進行讀取,電荷最終也會通過晶體管從電容器中洩漏出來,從而隨著時間的流逝而失去其明確定義的充電狀態。雖然定期刷新可以保持數據,但這也意味著需要讀取存儲器的內容並將其重新寫回。

為了讓DRAM更好地滿足未來市場需求,業界也在不斷地尋找新技術來突破目前的瓶頸,3D DRAM正是其中一個主流的技術方向。

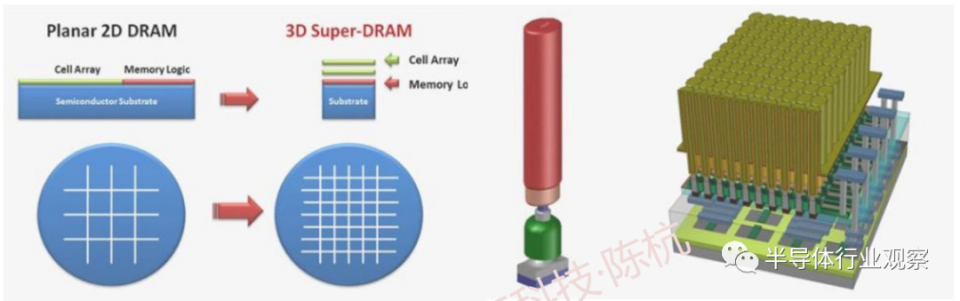

圖片來源:方正證券

據瞭解,3D DRAM是將存儲單元(Cell)堆疊至邏輯單元上方以實現在單位晶圓面積上產出上更多的產量,從這方面來說,3D DRAM 可以有效解決平面DRAM最重要也最艱難的挑戰,那就是儲存電容的高深寬比。儲存電容的深寬比通常會隨著組件工藝微縮而呈倍數增加,也就是說,平面DRAM的工藝微縮會越來越困難。

除了片晶圓的裸晶產出量增加外,使用3D堆棧技術也能因為可重復使用儲存電容而有效降低 DRAM的單位成本。因此,可以認為DRAM從2D架構轉向3D架構是未來的主要趨勢之一。

無電容IGZO,實現3D DRAM的候選者

當前在存儲器市場,能和DRAM“分庭抗禮”的NAND Flash早在2015年就已步入3D堆疊,並開始朝著100+層堆疊過渡,然而DRAM市場卻仍處於探索階段,為了使3D DRAM能夠早日普及並量產,各大廠商和研究院所也在努力尋找突破技術。

HBM(High Bandwidth Memory,高帶寬存儲器)技術可以說是DRAM從傳統2D向立體3D發展的主要代表產品,開啟了DRAM 3D化道路。它主要是通過硅通孔(Through Silicon Via, 簡稱“TSV”)技術進行芯片堆疊,以增加吞吐量並克服單一封裝內帶寬的限制,將數個DRAM裸片垂直堆疊,裸片之間用TVS技術連接。從技術角度看,HBM充分利用空間、縮小面積,正契合半導體行業小型化、集成化的發展趨勢,並且突破了內存容量與帶寬瓶頸,被視為新一代DRAM解決方案。

除了HBM外,研究者們也開始在無電容技術方面下功夫,試圖借此解決目前的難題。其實關於無電容,早有Dynamic Flash Memory、VLT技術、Z-RAM等技術出現,但日前,美國和比利時的獨立研究小組IMEC在2021 IEDM 上展示了一款全新的無電容器 DRAM,這種新型的DRAM基於 IGZO(indium-gallium-zinc-oxide)可以完全兼容 300mm BEOL (back-end-of-line),並具有>103s保留和無限 (>1011) 耐久性。

據介紹,這些結果是研究人員在為單個 IGZO 晶體管選擇最佳集成方案後獲得的,而這個最佳集成方案就是具有掩埋氧隧道和自對准接觸的後柵極集成方案。使用這種架構後,IGZO TFT(thin-film transistors)的柵極長度可以縮小到前所未有的 14nm,同時仍然保持大於100s的保留。通過EOT(equivalent oxide thickness)縮放控制閾值電壓 (Vt )、改善接觸電阻和減小IGZO層厚度,可以進一步優化小柵極長度下的保持率。當後者的厚度減小到 5nm 時,甚至可以省略O2 中的氧隧道和退火步驟,從而大大簡化了集成方法。

(a) 示意圖和 (B) 具有氧隧道和 14nm 柵極長度的後柵極架構中單個 IGZO 晶體管的 TEM 圖像

其實,在2020 IEDM上,imec就首次展示過這種無電容DRAM,並在當時掀起了一陣熱議。2020年消息顯示,當時這款DRAM包括兩個IGZO-TFTs並且沒有存儲電容,而這種2T0C(2晶體管0電容)DRAM架構還有望克服經典1T1C)(1晶體管1電容)DRAM 密度縮放的關鍵障礙,即小單元中 Si 晶體管的大截止電流尺寸,以及存儲電容器消耗的大面積。但在去年的“概念性”演示中,IGZO TFT 並未針對最大保留率進行優化,並且缺少對耐久性(即故障前的讀/寫循環次數)的評估。而今年這款無電容DRAM顯然在去年的基礎上進行了改進,保留率和耐久性都有了提高。

總的來說,今年新推出的新型DRAM 通過對基於 IGZO 的 DRAM架構和集成的改進,使2T0C DRAM 存儲器具有>10 3保留、無限耐久性和柵極長度縮小至 14nm。更重要的是,這些突破性的成果都使得無電容IGZO-DRAM 成為實現高密度 3D DRAM 存儲器的合適候選者。

IGZO TFT的壽命挑戰

對於傳統的2D技術來說,工藝製程不斷微縮逼近10nm極限是不小的挑戰。製程的微縮意味著光刻及蝕刻工藝所需的光罩數量不斷提高,圖案的分辨率很難得到保證。當工藝尺寸減小時,良率便無法得到控制,DRAM領域的bit growth從1994年至今一直處於下滑趨勢,增速從70%降低至20%。工藝升級速度減緩,尺寸工藝減小的進程也遇到了阻礙。

目前DRAM領域最為成熟的光刻技術是193nmDUV光刻機,其最大極限在大約10nm,而下一代13.5nmEUV光刻機是DRAM 工藝節點實現10nm以下突破的關鍵。引用此前一位網友的評論:“DRAM工藝不斷改進,按照一代工藝一代設備,又到了不斷加碼買設備的時間節點了。”

各大原廠紛紛有意引入分辨率更高的EUV光刻機來推動DRAM持續發展,但ASML 的EUV一年產能僅十幾台,難以滿足當前需求,而且價格也是極其昂貴。據瞭解,ASML亮相的新一代0.55NA EUV光刻機售價提高到19億元,高昂的售價使得EUV經濟效益低於DUV,同時如何將EUV技術投入量產也成為傳統2D技術面臨的難題之一。

而對於IGZO TFT來說,壽命問題或許是其未來發展的一大挑戰。目前為止,IGZO TFT 退化機制尚未被完全瞭解,因此缺乏用於預測基於 IGZO 的 DRAM 壽命的准確模型。針對這個問題,IMEC首次研究了柵極電介質對 IGZO TFT PBTI (positive bias temperature instability)的影響。

IGZO 晶體管本質上是 n 型器件,這表明PBTI可能是主要的退化機制。PBTI 是Sin型MOSFET中眾所周知的老化機制,會嚴重影響器件的性能和可靠性,通常表現為器件閾值電壓的不期望偏移和漏極電流的降低。然而,大多數現有的IGZO TFT 可靠性評估都忽略了柵極電介質的影響。

IMEC研究團隊發現四種不同的機制在降解過程中起作用,每種機制具有不同的時間動力學和活化能。它們主要歸因於柵極電介質中的電子捕獲,以及在 PBTI 應力期間氫物質從柵極電介質釋放到 IGZO 溝道。

基於不同柵極電介質的 IGZO TFT(具有 12 納米厚的非晶 IGZO 膜)的失效時間

目前,該研究團隊已將這些多種退化機制組合成一個模型,從而可以預測目標操作條件下的 IGZO TFT 壽命,可用於提出優化來提高壽命。

寫在最後

對於未來DRAM該怎麼走,其實研究者們已經提供了很多技術方向,但是目前均處於探索階段。基於PBTI的模型能否真的提升IGZO設備壽命;IGZO TFT 又能否使DRAM走向3D堆疊;3D堆疊是否真的可以為DRAM發展開辟新路徑,而這一切都需要市場來檢驗。

但可以肯定的是,隨著這些突破性技術的發展,DRAM 遠未走到生命盡頭,未來或將繼續稱霸存儲器市場。

*免責聲明:本文由作者原創。文章內容系作者個人觀點,半導體行業觀察轉載僅為了傳達一種不同的觀點,不代表半導體行業觀察對該觀點贊同或支持,如果有任何異議,歡迎聯系半導體行業觀察。

本文來自微信公眾號 “半導體行業觀察”(ID:icbank),作者:龔佳佳,36氪經授權發布。

本文經授權發布,不代表36氪立場。

如若轉載請註明出處。來源出處:36氪

Yahoo奇摩新聞

Yahoo奇摩新聞