【錯誤】 台積電的3奈米製程落後?大學電機系同學小陳訊息?誤導半導體技術

網傳「小陳是我大學電機系的同學」、「台積電的3奈米製程」、「武漢弘芯半導體已經能做到45奈米,而且即將進入90奈米」等半導體技術解釋訊息。對此 MyGoPen 透過新興科技媒體中心的協助,專家解釋實際上半導體製程的定義,一般而言多少奈米的製程,所代表的是單一電晶體的通道長度,通道長度越短,電晶體的導通速度越快。因此網傳貼文對技術的解讀是錯誤的。

台積電的3奈米製程與中芯技術的訊息

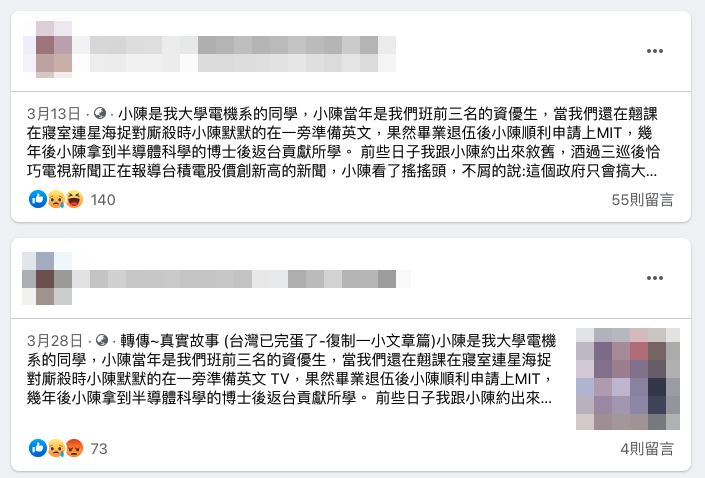

在社群平台流傳:

查證解釋:

對此,MyGoPen 透過新興科技媒體中心的協助,整理國立陽明交通大學電子工程學系暨電子研究所教授李鎮宜的回應,針對以下幾則訊息進行解析:

網傳貼文指出:學界評估半導體製程的難度,端看在一平方奈米的面積能放入幾個電晶體閘極;台積電的3奈米製程意味在1平方奈米的面積能放進3個電晶體閘極;中芯的技術已經到達28奈米,一平方奈米可以放28個電晶體閘極;武漢弘芯半導體已經能做到45奈米,而且即將進入90奈米。

半導體製程的定義是什麼?

半導體製程主要是將許多電晶體整合在單一晶片上,透過多層金屬導線,連結電晶體的輸入與輸出端,完成複雜的運算與儲存功能。

一般而言多少奈米的製程,所代表的是單一電晶體的通道長度,通道長度越短,電晶體的導通速度越快。

例如,長度為50奈米,只能放入小於50奈米的元件,5奈米的製程方式可放入十個電晶體,但若為7奈米製程,就只能放入七個電晶體。由此例可知奈米製程的數字高,不一定代表可放入較多電晶體。

什麼是高階的半導體製程? 半導體採用的製程愈高階,每單位面積晶片上的電晶體密度越高,運算能力與儲存功能也越高。

目前最新的半導體技術挑戰和趨勢為何?

目前挑戰有二:

1. 電晶體元件結構與二維絕緣材料的研發,在縮小元件尺寸的同時,亦能夠兼顧到節能省電,避免因過度耗電無法滿足行動裝置的使用規範。

2. 在單一晶片上製造十億、百億以上的電晶體,一方面確保製造過程無瑕疵,一方面又要確保效能可以不斷提升。

由於光刻機解析度代表能達到的最小奈米製程尺寸,所以目前晶圓代工產業最重要的是掌握極紫外光(EUV)的先進光刻機。

對此 MyGoPen 整理諮詢結論:

事實上尺寸越小,單位面積可以放的電晶體就越多,儲存的容量就會越高並能增快運算速度。

所以就需要更好的製程技術、機台以及製造服務,才能達到高良率、高毛利及高品質的大量生產 IC。

另外網傳 28 奈米到 90 奈米都是屬於舊產品技術,根據台積電邏輯製程的歷史資料,從 2004 年到 2011 年間就已進入量產。

因此網傳貼文對半導體製程技術的解讀是錯誤的。

資料來源:

新興科技媒體中心 - 網傳半導體技術有多強?專家解析半導體製程的實際意義

新興科技媒體中心 - 「半導體製程與技術的傳言」之專家意見 台積電 - 邏輯製程

Yahoo奇摩新聞

Yahoo奇摩新聞