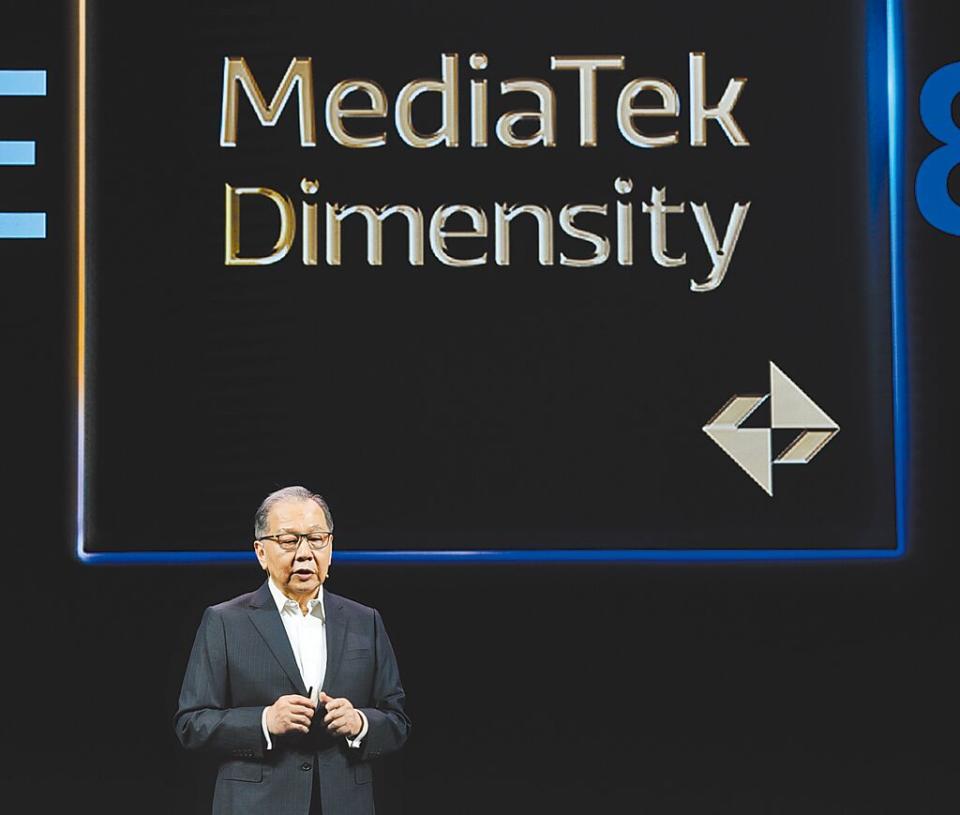

台版晶片法 聯發科籲放寬抵減上限

被稱為「台版晶片法」的《產業創新條例》第10-2條已經在5月31日受理截止,有4家業者遞件申請,預計在7月中下旬開始審查,外界原先認為晶圓代工龍頭台積電、IC設計龍頭聯發科有望申請適用,不過聯發科11日表示,希望能放寬抵減上限,更能發揮政策美意。

根據《產創條例》第10-2條規定,企業從事半導體研發費的25%以及使用先進製程設備的支出5%,可抵減當年度營所稅,並取消支出金額上限,不過申請的企業資格須符合年度研發費用支出達新台幣60億元、研發密度達6%、購置用於先進製程的設備支出達新台幣100億元,且2023年有效稅率為12%,並經過小組審查。

聯發科指出,IC設計業者主要投資項目為研發人員的薪資費用,非大規模的設備資本支出,若能參考像是南韓、美國、大陸等國家的擴大租稅抵減趨勢,去放寬個別研發以及設備抵減上限,相信更能發輝政策美意。

在過去10年,聯發科在台下單採購金額超過1.4兆元,最先進的技術、製程都在台灣下單,影響整體產業營利事業所得稅超過千億元,帶動產業鏈創造2千億以上的稅收貢獻。

產發署坦言,更動門檻的可能性不高,因為法已經擬定了。

智璞產業趨勢研究所執行副總林偉智指出,台灣在IC設計產業本來就存在相對優勢,那補助主要是拉抬劣勢的產業擴大生態系,且台灣的政府資源不像歐美或者大陸這麼豐富。聯發科最主要的資產以及支出就是人才,但那是基本支出並非資本支出,在大陸有補助,台灣雖然有但不多,所以政府如果有資源,還是希望可以補助這一塊。

Yahoo奇摩新聞

Yahoo奇摩新聞