強化我國優勢 IC設計攻頂補助將受理申請

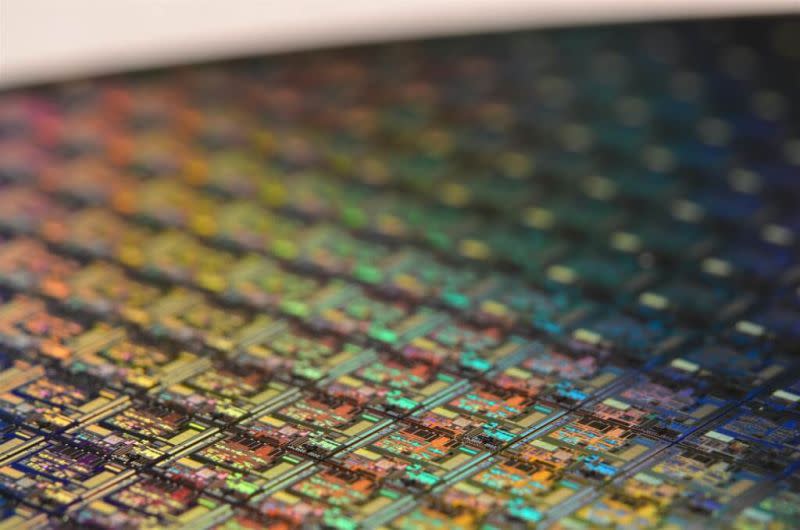

[NOWnews今日新聞] 台灣半導體業舉世聞名,除了晶片代工龍頭台積電,也不乏有聯發科、瑞昱及聯詠等IC設計,穩坐全球前3名寶座。經濟部技術司為了不斷強化我國IC設計量能,今(30)日公告,2025年「IC設計攻頂補助計畫」,將在2025年1月6日至2月27日期間受理申請。

據研調機構集邦科技(TrendForce)今年5月公告全球前十大IC設計廠排名,聯發科、聯詠、瑞昱躋身前十大廠。

經濟部長郭智輝今年6月也發願,台灣科技實力在AI時代扮演要角,將協助台灣IC設計廠商投入先進晶片、系統研發,目標推升IC設計業者在5年內進入全球前2名。

據公告,經濟部依據《經濟部協助產業創新活動補助獎勵及輔導辦法》第5條及第10條,以及行政院2023年所公告的「晶片驅動台灣產業創新方案」,將重點推動我國IC設計業者投入「具國際領先地位」之晶片及系統開發。

補助範疇包括,驅動台灣業者投入等同或超越國際標竿大廠技術指標之晶片設計開發、試產。

屬於自行開發晶片,優先鼓勵晶片廠商與系統應用業者共同提案,且申請補助計畫書應說明應用系統規格並完成相關驗證。

如果是若採外購晶片,強調創新應用,主要運算晶片須為國產晶片,且申請補助計畫書應列出完整期末系統驗證規劃並列為查核項目。

公告也提到,為了鼓勵我國企業規劃與開發,必須以下5個選項擇1項,分別為符合創新技術之晶片開發;異質整合封裝技術之創新晶片(小晶片整合封裝模組、矽光子等其他新興應用晶片開發);異質整合微機電感測技術之創新晶片開發,採用0.35μm以下之晶圓級製程;優先推動人工智慧、高效能運算、車用電子、下世代通訊等四領域,以及鼓勵運用AI技術並整合軟硬體,開發百工百業的應用系統,

而可以申請補助的業者,必須滿足補助我國晶片與系統應用業者為主,可由單一企業或多家企業聯合申請;申請廠商為國內依法登記成立之本國公司,含獨資、合夥、有限合夥事業或公司。

至於補助計畫期程為以不超過1年為原則。由本部籌組審查小組進行審查,核定通過後簽約執行,計畫執行期程可回溯至2025年3月1日。

經濟部也提醒,計畫申請時程為2025年1月6日至2月27日下午5點止;掛號郵件者以交郵當日郵戳為憑,親送或其他方式遞送者,須於2025年2月27日下午5點前送達為限。

除前列各項公告事項外,其他申請應備資料格式,及權利義務與注意事項等,詳見「IC設計攻頂補助計畫」申請須知。申請須知資料可由A+企業創新研發淬鍊計畫網頁(https://service.moea.gov.tw/EE514/tw/aiip/335.html)下載取得,或逕洽受理單位索取。

更多 NOWnews 今日新聞 報導

台積電壓尾盤、台股終場下跌21點 IC設計、機器人好熱!掀漲停潮

台積電衝高後拉回至平盤 鴻海、聯發科領頭!台股午盤漲83點

聯發科首辦「教學創新AI DAY」 落實科技扎根教育